In this article we will discuss Antenna Effect and ways to mitigate it. Antenna Effect is a physical phenomenon and related to geometry and fabrication process of the IC. So we will start with vertical cross section of an IC.

The above fig is showing the vertical cross section of a chip and which layer is included in which EOL.

That will help you to relate the EOLs and layers.Now lets discuss about End of Lines.

The whole CMOS fabrication process is divided into :

i. FEOL or Front End of Line :

In First End of Line we develop transistor level layout design on the wafer. The individual components like transistors , capacitors, resistors, etc. are fabricated in the semiconductor. FEOL consist of chemical mechanical polishing a.k.a Polarization and Cleaning of the wafer. Shallow Trench Isolation (STI) or LOCOS (tech node > 0.25 μm) comes under FEOL. FEOL also include well formation , gate module formation, Source and Drain module formation.

ii. MEOL or Mid End of Line :

In Middle End of Line or MEOL we do the transistor level interconnect. MEOL consist of semiconductor wafer processing steps that create local electrical connections among source/drain/gate of transistors. Most important part of MEOL is gate contact formation. Most important part of MEOL is gate contact formation. It occurs after Front-End-Of-Line (i.e transistors/design-capacitor/design-resistor formation) process are complete. Before Back-End-Of-Line metal/via/isolation-dielectric formation processes.

iii. BEOL or Back End of Line :

In Back End of Line we do the PnR level Interconnect through Metalization/Vias including Dielectric Separators among Various Metal layers.

Antenna Effect Phenomenon :

Let's understand what is antenna effect phenomenon. Now-a-days chemical etching has been completely replaced by hot plasma-etching.Plasma related process are used for CMOS flow for etching and deposition. The gaseous plasma contains charged particles inside. This charge gets transferred to the under-construction floating metals routes which may be connected way below up to the gate areas of MOSFET. At the same time such metals may not be connected to any diffusion areas in the FEOL Zone. Such metal wires act as “antennas” charge receptors that pick up electrical charge from the plasma gas. Charge accumulation on the metal strip is proportional to its length.

Now lets understand the antenna phenomenon during the process. As we can see from the above Fig, in the substrate Source (S) , Drain (D) , STI (Shallow Trench Isolation) is formed. Gate Oxide (G) and Poly Silicon layers grown and connected to Metal layer 1(M1). After the metal deposition the layer is etched as per mask. To do that plasma is used for etching. In this gaseous environment many charge get accumulated on the top of the M1 layer. Once this amount of charges is sufficiently high it causes breakdown of Gate Oxide insulator and the charges pass on to the Silicon substrate.

Now we will dig deeper into the phenomenon and will try to understand it in a better way. Aforementioned metal wires builds up high potential difference on the metal side through piled up charge. As a consequence high electric field builds up across the gate oxide of the Metal-Oxide-Semiconductor (MOS) structure.Sufficient accumulation charge create a percussion path through oxide for drainage of charge. This percussion path is a small path that is created by the high amount of charge and this is just the beginning. Severe drainage in MOSFET lead to the gate oxide break-down, consequently damaging the MOSFET. On the other hand in case less severe drainage the MOSFET is not damaged, although Hot Carrier Injection (HCI) may take place. HCI will cause faster aging and MOSFET performance will get degraded in the long run.

Semiconductor CMOS Process :

Antenna violation occurs due to use of plasma in CMOS fabrication. SO let's take a recap of the fabrication steps. The fabrication process of VLSI Integrated Circuits (IC) consists of a set of basic steps starting from crystal growth, wafer preparation, epitaxy, dielectric and poly Si film deposition, oxidation, lithography, and dry etching. Different patterns are developed by repeating steps like deposition, photo resist coating, exposure, developing, etching, ion implantation and stripping etc as shown in the above Fig. These steps are repeated in cyclic order several times for formation of metal routes in the BEOL region. FEOL and MEOL also goes in this cyclic steps although BEOL goes several times. The step etching is done by using plasma and in this step antenna violation may occur. Not only 1st Metal layer, this violation may occur to any metal layer.

Different Types of Plasma Process :

There are three different plasma process involved in VLSI

CMOS process -

1. Conductor Layer Pattern Etching Processes

2. Ashing Processes

3. Contact Etching Processes

1. Conductor Layer Pattern Etching Processes :

Etching processes splits conductor layer plates into multiple routing patterns.Here the amount of accumulated charge is proportional to the perimeter length of conductor area. Perimeters of the spitted routing are directly exposed to plasma.

2. Ashing Processes :

Ashing processes remove remaining photo resist layer after etching processes of conductor layer.Here the amount of accumulated charge is proportional to the area of the conductor layer patterns. Area of conductor layer patterns is directly exposed to plasma.

3. Contact Etching Processes:

Contact etching processes dig holes between two conductor layers. Here the amount of accumulated charge is proportional to the area of the total area of the contacts. Here the area of all the contacts on the lower conductor layer pattern is directly exposed to plasma.

Metals/Via Stacks are built layer by layer. First, Metal1 is deposited and all unwanted portions are etched away by plasma etching. The metal geometries when they are exposed to plasma can collect charge from it. Once Metal1 is completed, Via1 is built, then Metal2 and so on. So with each passing stage, the metal geometries can build up static electricity. If the charge collected is large enough to cause current to flow to the gate, this can cause damage to the gate oxide. Long metal lines are prone to such failures ending into fabrication yield.

Nonuniform density of plasma across the wafer plays an important role in antenna related damage. Such non-uniformity can come from non-uniformity in radio frequency (RF) current flow, electron current flow and ion current flow. In addition to this , Electron shading effect can contribute in plasma charging. This plasma charging(metal) & discharging(through oxide) can severely degrade or destroy devices, especially Metal Oxide Semiconductor (MOS) gate dielectrics. This particular problem is becoming more prominent in lower technology node with thinner gate oxide. The gate oxide degradation occurs by Fowler-Nordheim (FN) tunnel injection between the gate oxide and the silicon substrate.

In the continuous plasma exposure environment, the gate potential build-up adjusts itself by the FN tunneling current. The flow of tunneling current generates trap and interface states in the gate oxide, gradually degrading the oxide quality and integrity. At very high level of stress or prolonged exposure, it may also ultimately lead to the breakdown of the oxide. In high-aspect ratio spaces, isotropic electrons are hindered from reaching the bottom of the space, whereas anisotropic and positively charged ions are not. This is phenomenon is called "electron shading" which happens in uniform plasma when topography exists on the wafer during plasma exposure.Insulators such as photo-resist or oxides are commonly used as masks when etching conductive films. The underlying conductor can acquire a positive charge by the electron shading mechanism.

Antenna Ratio :

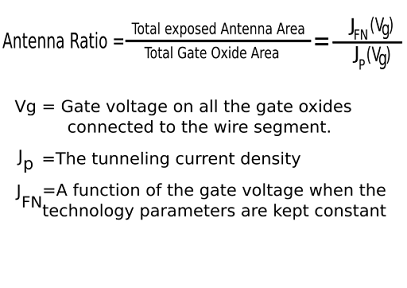

The magnitude of the accumulated charge depends on the ratio of the floating conducting region area to the gate area. This is called the Antenna Ratio and quoted in Design Rule Manual.

The above equation shows the relationship between the antenna ratio and the current densities. A higher antenna ratio means a larger Vg and, thus more damage.