Power Dissipation in DSM/Nano Era :

Portable computers, wearable electronics gadgets, wireless devices have become much more popular recently. Earlier portable devices didn't need much computing power. Power requirement of state-of-art portable devices are comparable to their non-portable counterparts. For real time use scenario batteries must last longer. Making batteries that runs longer is an one big challenge. Figuring out how to manage power use is another big challenge. Power dissipation becoming more and more prominent issue. It's harder to deal with the heat and keep things cool because the amount of power being used in a given area is increasing. Integrated circuit is composed by : sequential ckt. , combinational ckt., memory blocks and I/O devices. All have different power consumption rate.

Power consumption in the logic circuits :

1. 40 % in sequential blocks ,

2. 30 % in combinational parts ,

3. 20% in memory blocks,

4. 10% in I/O devices.

Sources of Power Dissipation :

Power consumption is determined by : frequency f, supply voltage V, capacitance C, leakage, and short circuit current. Two types of power dissipation : (i) Dynamic & (ii) Static Power dissipation.

Dynamic power dissipation: When a circuit is in active state or in use , power dissipation due to change in input is called dynamic power dissipation. Dynamic power dissipation is total outcome of switching power, short circuit power and glitching power dissipation.

Static Power Dissipation: Static power is the power dissipated when the gates are idle or there is no output transition. Static power dissipation is caused by leakage currents. Static Power Consumption related to each gate extremely small although summation of all gates become a significant figure.

Dynamic Power Dissipation

Switching Power Dissipation :

Dynamic switching power dissipation is caused by charging and discharging of O/P capacitors in the circuit

1. I/P changes from high-to-low i.e 1→0

2. O/P changes from low-to-high, i.e. 0→1

3. PMOS/pull up transistor is ON

4. NMOS/pull down transistor will be OFF

5. Capacitor CL charges through pull up transistor.

6. Charging energy is drawn from the power supply.

7. Part of this energy is dissipated in PMOS device and part is stored on CL.

1. I/P changes from low-to-high i.e. 0 →1

2. O/P changes from high-to-low, i.e. 1→0

3. PMOS/pull up transistor is OFF

4. NMOS/pull down transistor will be ON

5. Capacitor CL discharges through pull down transistor, and power will be dissipated at pull down transistor.

Short Circuit Power Dissipation :

Short circuit power dissipation is generated by the short circuit current flowing through both the nMOS and the pMOS transistors during switching. The short circuit current occurs if a logic gate is driven by the input voltage wave forms with the finite rise and fall times. Thus both the nMOS and the pMOS transistors in the circuit conduct simultaneously for a short period of time during the transitions, forming a direct current path between the power supply and ground. This power dissipation takes place even when there is no load or input parasitic capacitor. Short circuit power dissipation depends on mobility of electrons,channel width& length of transistor, supply and threshold voltage, transition time i.e. rise and fall time of input voltage and frequency of operation.

Glitching Power Dissipation :

Glitching power dissipation occurs due to finite delay. This Power dissipated in the intermediate transitions during the evaluation of the logic function of the circuit. In multi-level logic circuits, the propagation delay from one logic block to the next can cause the input signals to the block to change at different times. Thus, a node can exhibit multiple transitions in a single clock cycle before settling to the correct logic level. These intermediate erroneous outputs lead to a power loss in charging and discharging the output load capacitance. This can reduce by using tree logic structures instead of chain logic structures.

Static Power Dissipation

Static Power Components:

Static power is caused by leakage currents while the gates are idle i.e , when there is no output transitions. Ideally CMOS gates should not be consuming any power in this mode. In reality, however, there is always some leakage current passing through the transistors, indicating that the CMOS gates do consume a certain amount of power. Static power consumption, associated with each logic gate is extremely small although the total effect becomes significant when tens of millions of gates are utilized in state-of-art ICs. With decreasing feature size , leakage is increasing. Different components of leakage current :

1. Reverse Diode Leakage Current (I1)

2. Sub-threshold Leakage Current (I2)

3. Drain-Induced Barrier-Lowering Effect (I3)

4. Gate Induced Drain Leakage Current (I4)

5. Punch Through (I5)

6. Gate Oxide Tunnelling Current (I6)

7. Hot Carrier Injection (I7)

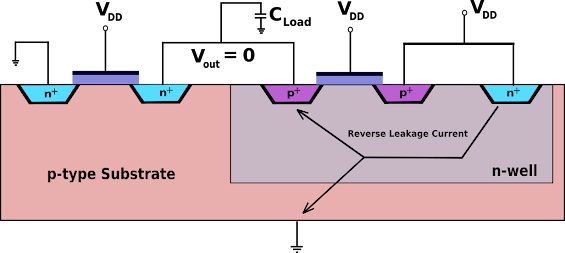

Reverse Diode Leakage Current:

The reverse diode leakage occurs when the p-n jn. between the drain and the bulk of the transistor is reverse-biased. The reverse-biased drain junction conducts a reverse saturation current which is drawn from the power supply. Reverse leakage current is expressed as:

Vbias is the reverse bias voltage across the jn. , JS is the reverse saturation current density, and A is the junction area. Since the leakage current is proportional to the junction area, it is advisable to minimize the area as much as possible in the layout. The reverse saturation current density is exponentially proportional to the temperature.

Sub-threshold Leakage Current:

Also known as the weak inversion current. Current flows from drain to source. Occurs when the gate voltage is below the threshold voltage VTh. The sub-threshold leakage current can be approximately formulated as:

Where μ0 is the zero bias mobility, Cox is the gate oxide capacitance, and (W/L) represents the width to the length ratio of the leaking MOS device. VT is the thermal voltage constant, and Vgs represents the gate to the source voltage. The parameter η in eqn subthreshold swing co-efficient given by 1 + Cd/Cox with Cd being the depletion layer capacitance of the source/drain junction. Sub-threshold leakage current is exponentially proportional to (Vgs-VTh). Traditionally, the threshold voltage VTh has been high enough that with Vgs = 0, the sub-threshold current is very small. With state-of-art technology node, reduced power supply voltages require the VTh to be reduced also, and thus, the sub-threshold leakage at Vgs = 0 becomes significant. Sub-threshold leakage can be reduced by increasing the VTh or reducing the Vgs. However, increasing the VTh affects performance, so there is a strong trade off between performance and the power dissipation of a design.

Drain-Induced Barrier-Lowering Effect (I3):

Gate-Induced Drain Leakage (I4):

The GIDL current arises in the high electric field under the gate/drain overlap region which causes a depletion. GIDL occurs at a low VG and high VD bias and generates carriers into the substrate and drain from the surface traps. Generates carriers into substrate from surface traps, band-to-band tunneling Localized along channel width between gate and drain Seen as “hook” in I-V characteristic causing increasing current for negative VG - Thinner oxide, higher VDD, lightly-doped drain enhance GIDL

Punch Through (I5) :

Its a break down mechanism. Occurs when the sum of depletion layer width for source and drain junctions is comparable to the channel length. The depletion region of the drain and source junctions gradually merge together as the drain voltage is increased, causing current to flow irrespective of Vg at high Vd. Gate loses control. Current varies quadratically with drain voltage.

Gate Oxide Tunneling (I6):

High E-field Eox can cause direct tunneling through gateoxide or Fowler-Nordheim (FN) tunneling through oxide bands - Typically, FN tunneling at higher field strength than operating conditions. Significant at Tox < 5 nm - Become dominant leakage mechanism as Tox get thinner - High K dielectrics is alternative.

Hot-Carrier Injection(I7):

Hot carrier is a generic name for high-energy hot electrons and holes generated in the transistor. Hot Carrier is easily generated when the Vg < Vd/2 . When Vd> Vg, the carriers present in the channel will impact the Si crystal lattice and generate pairs of a hot electron and a hot hole (Impact Ionization). These pairs function as hot carriers. Hot carriers under strong Vd gain enough energy to break the barrier of Si/SiO2 inrterface and go through the gate oxide into the gate. As a result, either the gate oxide film is charged, or the Si-SiO2 interface is damaged. This lead to change is transistor characteristic .

Generation mechanism :

1. Channel hot electrons (CHE),

2. Avalanche hot carriers (AHC),

3. Substrate hot electrons (SHE).

AHC shows remarkable change when devices are miniaturized.

Why Leakage Power is an Issue?

Leakage power increases at faster rate than dynamic power (active power) in technology generation and it becoming a large component of total power dissipation. In standby applications leakage power component becomes a significant % of the total power. Earlier leakage power during standby mode is important to reduce but reduction of runtime leakage power is important in deep submicron technology.

Watch the video lecture here :