The article delves into crucial aspects of power optimization in CMOS circuits. In this atricle, we have explored various strategies for optimizing power in electronic circuits comprehensively. We started with an overview of power optimization circuits, touching on key low power design methodologies and examining the extensive power reduction design space. We delved into the concept of power states, discussing techniques such as voltage scaling, multi-voltage scaling, and power gating, which are crucial for reducing power consumption. Further, we covered clock tree optimization and clock gating, as well as advanced transistor techniques like dual, multi, and variable threshold MOSFETs and transistor stacking. The discussion also included the use of special cells for power optimization, interconnect strategies, and the tools available for implementing these power optimization techniques.

Low Power Design Methodologies :

Whatever power goes inside the IC comes out as heat. Continues current flow in the circuit increases junction temperature and that heat must be dissipated. That dissipation happens through the packaging. Power optimization in IC is a must otherwise the heat dissipation If the chip Packaging and its costs, Power supply rail design,

- Chip and system cooling costs

- Noise immunity and system reliability

- Battery life (in portable systems)

In VLSI design circuit speed has been considered as performance metric. Power considerations has become ultimate design criteria in portable applications. Aim of these applications is to maximize battery life time, with minimum power. LPD also need to reduce the power in high-end systems with huge integration density and thus improve the speed of operation. Digital systems design is spread over multiple steps from system to process level. To optimize power (specifically for LPD), the method should be applied over all steps. It is very important to have knowledge about the power distribution. So the blocks or parts consuming fraction of power could be clearly optimized for saving power.

Power Reduction Design Space :

1. Power reduction through system integration :

- Utilize low system clocks

- Use high level of integration

- Integrating off-chip memories (ROM, RAM, etc.) and other ICs such as digital and analog peripherals.

2. Power reduction by algorithm level :

- Minimizing the number of operation. That reduces the number of H/W resources

- Data coding for reduce the switching activity.

3. Power reduction through architectural model :

- Power management by shutting down unused blocks

- Low-power architectures based on parallelism, pipelining, etc.

- Memory partition with selectively enabled blocks

- Reduction of the number of global busses

- Minimization of instruction set for simple decoding and execution.

4. Power reduction through circuit/logic design :

- Reduce switching activity by optimized algorithm

- Optimize clock and bus loading

- Circuit techniques which minimizes number of devices used in the circuit

- Custom design may improve the power

- Reduces VDD in non-critical paths and proper transistor sizing

- Use of multi-VT circuits

5. Power reduction through process technology :

- One way to reduce the power dissipation is to reduce the power supply voltage. Reduction in Vdd increases delay. To match the device with supply voltage scaling is the option.

- The advantages of scaling for LPD are : improved current drive capabilities,

reduced capacitances through small geometries and junction capacitances

- Improved interconnect technology

- Availability of multiple and variable threshold devices

- This results In good management of active and standby power trade-off

- Higher density of integration.

What are Power States :

Depending on functional role of an IP, Power states are defined and power is saved. Power states are defined and differentiated from each other based on corresponding functional mode. Based on usage power is reduced and saved. In some cases, power states can have sub-states.

Voltage Scaling :

Supply Voltage Scaling :

Used to reduce dynamic and leakage power. Lowers subthreshold current and gate leakage current. The optimal point for power savings using this technique is the lowest voltage which the circuit retains its logic states and does not compromise performance. To achieve low-power benefits without compromising performance, two ways of lowering supply voltage can be employed: the static supply scaling and the dynamic supply scaling.

Static Supply Scaling: ( Voltage Islands)

Multiple supply voltages are used as per operation requirement. Critical and non-critical paths and/or units re clustered and powered accordingly. Whenever an output from a low Vdd unit has to drive an input of a high Vdd unit, a level conversion is required at the interface.

Dynamic Supply Scaling :

This technique uses single supply voltage. Hence cost is less. When performance demand is low, supply voltage and clock frequency are lowered. Substantial power reduction is possible by that. Circuit need to be operable over a wide voltage range. Operating system to intelligently determine the processor speed. Regulator to generate the minimum voltage for specific speed.

Multi Voltage Scaling :

Dynamic Voltage and Frequency Scaling (DVFS):

A larger number of voltage levels are dynamically switched to follow changing workloads.

Adaptive Voltage Scaling (AVS):

An extension of DVFS where a control loop is used to adjust the voltage.

Multi-Voltage Design Challenges :

1. Level shifters: Signals that go between blocks that use different power rails require level shifters.

2. Characterization and STA: Need libraries for each voltage and level shifter configuration.

3. Floorplanning: Complex power planning and power grids

4. Board level issues: Need additional regulators to provide the additional supplies.

5. Power up and power down sequencing: There may be a required sequence for powering up the design.

Power Gating :

One of the technique to reduce the leakage power. In this technique a MOSFET switch or sleep transistor is used to cut off/gate, a circuit from the power rails (Vdd and/or gnd) during standby mode. The switch typically is positioned as header between the circuit and the Vdd or as footer between the circuit and the ground. Power gating has the basic strategy of providing Sleep/Stand By mode & Active mode. During active operation, the power gating switch remains on, supplying the current that the circuit uses to operate. During standby mode, turning off the power gating switch reduces the current dissipated through the circuit.

Clock Tree Optimization & Clock Gating :

Clock signal is the most fundamental signal for any digital circuit and Clock signal consumes the most amount of the total power. The design of clock network is important in order to make the low power system achieve good functional stability under low voltage. Clock distribution is crucial for timing and design convergence. Most of the power is consumed due to the high clock frequency used for operating the device. Up to 70% or even more of the dynamic power can be spent in the clock buffers. This is a critical problem in every synchronous circuit. Portions of the clock tree that are not being used at any particular time can be disabled to save the power. This is clock gating and its an effective way of reducing the dynamic power dissipation.

One of the ways to achieve this is by masking the clock that goes to the idle portion of the circuit. Clock gating is particularly useful for registers that need to maintain the same logic values over many clock cycles. The main challenges of clock gating are finding the best places to use it and creating the logic to shut off and turn on the clock at the proper times.

Dual/Multi/Variable Vth MOSFET :

The present-day process technology allows the fabrication of MOSFETs of multiple Vt on a single chip. Dual-Vt CMOS circuits is used for high-performance and low-power CMOS circuits. High-Vt transistors used to reduce leakage current and low-Vt transistors to achieve high performance. There are various fabrication technique for implementing multiple Vt MOSFETs in a single chip.

1. Multiple Channel Doping : Commonly used technique for realizing multiple-VT MOSFETs is to use different channel doping densities

2. Multiple Oxide CMOS : Vth has a dependence on the value of Cox. Different Cox can be realized by using different Tox and accordingly Vth will be different.

3. Multiple Channel Length : Vth decreases as the channel length is reduced, known as Vth roll-off. This phenomenon is exploited to realize transistors of dual threshold voltages.

4. Multiple Body Bias : When the substrate and the source has a voltage difference that leads to an increase or decrease of the threshold voltage.

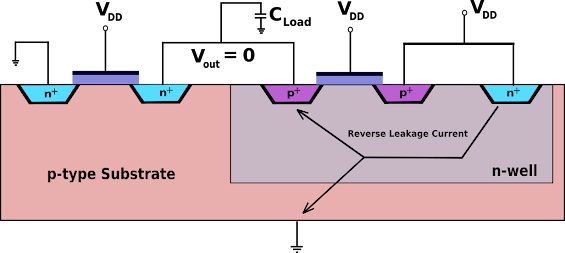

Multi-Threshold CMOS (MTCMOS) is a popular power gating approach that uses high Vth devices for power switches . Variable threshold CMOS is a body biasing based design technique.

Transistor Stacking :

Subthreshold leakage current flowing through a stack of series connected transistors reduces when more than one transistor in the stack is turned off. This effect is known as “stacking effect”. Consider a two transistor stack. When both M1 and M2 are turned off, the voltage at the intermediate node (Vx) is positive due to a small drain current.

Positive potential at the intermediate node has three effects:

1. Due to the positive source potential Vx, gate-to-source voltage of transistor M1 (Vgs1) becomes negative; hence, the subthreshold current reduces substantially.

2. Due to Vx > 0, bulk-to-source potential (Vbs1) of transistor M1 becomes negative, increasing the threshold voltage (Vth) (larger body effect) of M1, and thus reducing the subthreshold leakage.

3. Due to Vx > 0, the drain-to-source potential (Vds1) of transistor M1 decreases,increasing Vth (less DIBL) of M1, and thus reducing the subthreshold leakage. The leakage of a two-transistor stack less than the leakage in a single transistor.

Special Cells & Power Optimization :

1. Retention Cell :

Memories or registers are not capable of keeping their information while powered off. When a particular power domain inside chip is switched off, it is bound to loose its memory. To save such scenarios special retention cells have been adopted in most of the commercial standard cell libraries (eg. TMSC, UMC, GF), to support the State retention power-gating (SRPG). Retention cells store the last state before power off of a flop inside the power domain. Thus it allows the system to continue its operation from the last known state and faster wake up of a block. The only Drawback is the Retention Mode consumes little more current than power off mode.

2. Isolation Cell :

Inter-domain signals can become complicated if the connecting interface changes during different power modes. During Power Gating operation, the circuit will contain few ON and OFF domains together at any point of time. In such situation, output of a OFF domain sends invalid signal to the ON Domain. To deal with such problematic situation Isolation Cell is placed between power gated block and the active block. An Isolation Cell clamps the signal at its input pin to a defined known state, either logic "0 ‟ or logic "1". Hence transmission of invalid signal is eradicated.

3. Level Shifters Cell :

In multi voltage/power domain system, the logic gates on noncritical paths are operated with low VDD and gates on critical path are operated with high VDD. Chip with different supply voltage domains use level shifters to convert and propagate logic signals among different power domains.

4. Always On cells :

Interconnect & Power Optimization :

Interconnect-power reduction : A circuit consumes switching power Pswitch when the interconnection capacitances are charged and discharged. The interconnect power occupied more than half of the total dynamic power consumption Pdynamic ,with 90% of it contributed from 10% of the interconnections. To reduce Cdyn , larger wire spacing and minimal length routing were implemented for the high-power consuming interconnects.

Net ordering and wire space optimization :To optimize power consumption, interconnect capacitance must be reduced. That can be achieved by rearranging the wire positions I.e net ordering and wire space optimization. Signals with high switching activity (SA) share a relatively larger space than those with lower SA .

Tools & Power Optimization :

Commercial EDA tools effectively support power management techniques. They also provide additional power savings during implementation. Low power VLSI designs can be achieved at various levels of the design abstraction from algorithmic and system levels down to layout and circuit levels. Varieties of power analysis tools are available to estimate the power of a design. All commercial tool vendor have such tools. The power products are tools that comprise a complete methodology for low power design. Such tool offers power analysis and optimization from RTL to the gate level. Some tool provides transistor-level power analysis. Activity/switching rate are the basis of analysis for some power tools. In traditional flow each tool has their own low power design commands although there core description might be inconsistent. UPF is used in all tools for obtaining consistent low power consumption design requirements. Tools can be automatically inserted according to UPF description during FE integration. MTCMOS is inserted and connected in rear-end realization tools. Complex power connection, control signal connection are automatically realized according to UPF description. The operation is simple and convenient with high accuracy.

Watch the video lecture here :

X

Courtesy : Image by www.pngegg.com